**User's Manual**

# NEC

# $\mu$ PD172×× Subseries

# **4-bit Single-chip Microcontroller**

**Common Functions**

| μ <b>ΡD17201A</b> | $\mu$ PD17227   |

|-------------------|-----------------|

| μ <b>ΡD17203A</b> | $\mu$ PD17228   |

| μ <b>ΡD17204</b>  | $\mu$ PD17P203A |

| μ <b>ΡD17207</b>  | $\mu$ PD17P204  |

| μ <b>PD17225</b>  | $\mu$ PD17P207  |

| μ <b>ΡD17226</b>  | $\mu$ PD17P218  |

Document No. U12795EJ4V0UM00 (Previous No. IEU-1317B) Date Published June 1998 N CP(K)

© NEC Corporation 1991 Printed in Japan

# NOTES FOR CMOS DEVICES -

# **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# ② HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

SIMPLEHOST and *emIC-17K* are trademarks of NEC Corporation. PC/AT is a trademark of IBM Corporation. Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries. The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

# The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

# NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

# NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

# **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

NEC Electronics (France) S.A. Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

# **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 **NEC Electronics Hong Kong Ltd.** Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 65-253-8311 Fax: 65-250-3583

**NEC Electronics Taiwan Ltd.** Taipei, Taiwan Tel: 02-719-2377

Fax: 02-719-5951

# NEC do Brasil S.A.

Cumbica-Guarulhos-SP, Brasil Tel: 011-6465-6810 Fax: 011-6465-6829

# MAJOR REVISIONS IN THIS EDITION

| Page       | Contents                                                                             |

|------------|--------------------------------------------------------------------------------------|

| Throughout | μPD17225, 17226, 17227, and 17228 added                                              |

| Throughout | μPD17202A, 17215, 17216, 17217, 17218 and 17P202A deleted                            |

| Throughout | Assembler changed (AS17K $\rightarrow$ RA17K)                                        |

| p. 20      | Changes in 1.1 List of Functions                                                     |

| p. 137     | Extension instruction added to the table in 15.4 Assembler (RA17K) Macro instruction |

| p. 201     | A.1 Hardware List modified                                                           |

| p. 202     | A.2 Software List modified                                                           |

The mark  $\bigstar$  shows the major revised points.

# INTRODUCTION

| Targeted reader         |                                                                                                                   | for the users who understand the functions of the $\mu$ PD172×× rs and design application systems using these microcontrollers.                                                                                                                                                                                                                                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective               |                                                                                                                   | the functions common to all the models in the $\mu$ PD172×× e as a reference manual when you develop a program for a crocontrollers.                                                                                                                                                                                                                                             |

| How to read this manual | It is assumed that the rea<br>engineering, logic circuit                                                          | ders of this manual possess general knowledge about electric as, and microcomputers.                                                                                                                                                                                                                                                                                             |

|                         | <ul> <li>To understand the ov</li> <li>→ Read this manual</li> </ul>                                              | rerall functions of the $\mu$ PD172×× subseries, using the Contents.                                                                                                                                                                                                                                                                                                             |

|                         |                                                                                                                   | nction of an instruction whose mnemonic is known,<br>X C INSTRUCTION INDEX.                                                                                                                                                                                                                                                                                                      |

|                         | whose function is kno                                                                                             | nction of the instruction whose mnemonic is not known but<br>own,<br>ruction List by referring to 15.5 Instruction Functions.                                                                                                                                                                                                                                                    |

|                         |                                                                                                                   | I specifications of the $\mu$ PD172×× subseries,<br>Sheet for the respective models.                                                                                                                                                                                                                                                                                             |

| Legend                  | Data significance<br>Active low<br>Memory map address<br><b>Note</b><br><b>Caution</b><br><b>Remark</b><br>Number | <ul> <li>Higher digit on left, lower digit on right</li> <li>xxx (bar over pin and signal names)</li> <li>Top-low, bottom-high</li> <li>Description of Note in the text.</li> <li>Information requiring particular attention</li> <li>Supplementary explanation</li> <li>Binary xxxx or xxxxB</li> <li>Decimal number xxxx or xxxxD</li> <li>Hexadecimal number xxxxH</li> </ul> |

Refer to the following documents (the numbers in this table indicate the document number).

| Part Number                                                             | μPD17201A                     | μPD17207                       | μPD17P207            | μPD17203A             | μPD17P203A           | μPD17204              | μPD17P204            |

|-------------------------------------------------------------------------|-------------------------------|--------------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|

| Data sheet                                                              | U11778J<br>[U11778E]          |                                | U11777J<br>[U11777E] | IC-8089<br>[U10334E]  | IC-8303<br>[IC-2851] | IC-8089<br>[U10334E]  | IC-8303<br>[IC-2851] |

| Instruction table                                                       | IEM-5537 [IE                  | EM-1213]                       |                      | IEM-5544              |                      |                       |                      |

| User's manual                                                           | U12795J [U <sup>.</sup>       | 12795E](This                   | manual)              |                       |                      |                       |                      |

| Application note                                                        | IEA-707 [IEA                  | \-1285]                        |                      | _                     | _                    | _                     | —                    |

|                                                                         | IEA-757 [IEA<br>(Floating-poi | A-1306]<br>int arithmetic      | package)             | _                     | _                    | _                     | _                    |

| SE board<br>user's manual                                               | EEU-763<br>[EEU-1372]         |                                |                      | EEU-762<br>[EEU-1371] |                      |                       |                      |

| Device file<br>user's manual                                            | EEU-736<br>[EEU-1373]         | EEU-746<br>[EEU-1360]          |                      | EEU-738<br>[EEU-1350] |                      | EEU-751<br>[EEU-1361] |                      |

| Microcontrollers for remote controllers selection guide                 | X10088J<br>[X10088E]          |                                |                      |                       |                      |                       |                      |

| 17K series/DTS standard models selection guide                          | U10317J<br>[U10317E]          |                                |                      |                       |                      |                       |                      |

| RA17K<br>user's manual                                                  | U10305J<br>[U10305E]          |                                |                      |                       |                      |                       |                      |

| IE-17K/IE-17K-ET<br>CLICE/CLICE-ET<br>user's manual                     | U10063J<br>[U10063E]          |                                |                      |                       |                      |                       |                      |

| <i>SIMPLEHOST</i> ™<br>user's manual                                    |                               | troduction [E<br>eference [EE  |                      |                       |                      |                       |                      |

| SIMPLEHOST<br>emIC-17K <sup>TM</sup> /RA17K compatible<br>user's manual |                               | ntroduction [l<br>Reference [U |                      |                       |                      |                       |                      |

| Project manager<br>user's manual                                        | U12810J<br>[EEU-1527]         |                                |                      |                       |                      |                       |                      |

| MAKE/CNV17K<br>user's manual                                            | U10596J<br>[U10596E]          |                                |                      |                       |                      |                       |                      |

| <i>emIC-17K</i><br>user's manual                                        | EEU-876<br>[EEU-1511]         |                                |                      |                       |                      |                       |                      |

| LK17K<br>user's manual                                                  | U12518J<br>[U12518E]          |                                |                      |                       |                      |                       |                      |

| DOC17K<br>user's manual                                                 | EEU-5006<br>[EEU-1536]        |                                |                      |                       |                      |                       |                      |

# • 4-bit single-chip microcontrollers ( $\mu$ PD172×× subseries) (1/2)

**Remark** The number inside [] indicates document number for English version.

# • 4-bit single-chip microcontrollers ( $\mu$ PD172 $\times\!\times$ subseries) (2/2)

| Part Number                                              | μPD17225                            | μPD17226                            | μPD17227 | μPD17228 | μPD17P218             |

|----------------------------------------------------------|-------------------------------------|-------------------------------------|----------|----------|-----------------------|

| Item                                                     |                                     |                                     |          |          |                       |

| Data sheet                                               | U12643J<br>[U12643E]                |                                     |          |          | U12217J<br>[IC-3252]  |

| Instruction table                                        | _                                   | —                                   | —        | _        | _                     |

| User's manual                                            | U12795J [U1279                      | 5E] (This manual)                   |          |          |                       |

| Application note                                         | _                                   | _                                   | _        | _        | _                     |

| SE board<br>user's manual                                | U12372J<br>(U12372E)                |                                     |          |          | _                     |

| Device file<br>user's manual                             | U12136J<br>(U12136E)                |                                     |          |          | EEU-925<br>[EEU-1461] |

| Microcontrollers for remote controllers selection guide  | X10088J<br>[X10088E]                |                                     |          |          |                       |

| 17K series/DTS standard models selection guide           | U10317J<br>[U10317E]                |                                     |          |          |                       |

| RA17K<br>user's manual                                   | U10305J<br>[U10305E]                |                                     |          |          |                       |

| IE-17K/IE-17K-ET<br>CLICE/CLICE-ET<br>user's manual      | U10063J<br>[U10063E]                |                                     |          |          |                       |

| SIMPLEHOST<br>user's manual                              | EEU-723: Introdu<br>EEU-724: Refere |                                     |          |          |                       |

| SIMPLEHOST<br>emIC-17K/RA17K compatible<br>user's manual | EEU-5009: Introd<br>EEU-5007: Refer | luction [U10445E]<br>ence [U10496E] |          |          |                       |

| Project manager<br>user's manual                         | U12810J<br>[EEU-1527]               |                                     |          |          |                       |

| MAKE/CNV17K<br>user's manual                             | U10596J<br>[U10596E]                |                                     |          |          |                       |

| <i>emIC-17K</i><br>user's manual                         | EEU-876<br>[EEU-1511]               |                                     |          |          |                       |

| LK17K<br>user's manual                                   | U12518J<br>[U12518E]                |                                     |          |          |                       |

| DOC17K<br>user's manual                                  | EEU-5006<br>[EEU-1536]              |                                     |          |          |                       |

**Remark** The number inside [] indicates document number for English version.

# [MEMO]

# TABLE OF CONTENTS

| CHAPTE | R 1 GE  | NERAL                                                                      |

|--------|---------|----------------------------------------------------------------------------|

| 1.1    | List of | Functions 20                                                               |

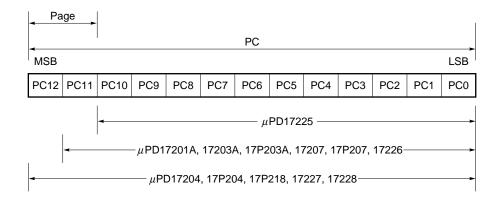

| СНАРТЕ | R 2 PR  | OGRAM COUNTER (PC) 23                                                      |

| 2.1    | Progra  | am Counter Configuration                                                   |

| 2.2    | Progra  | am Counter Operations 24                                                   |

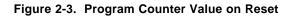

|        | 2.2.1   | On reset                                                                   |

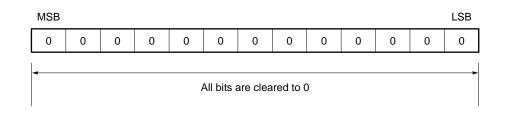

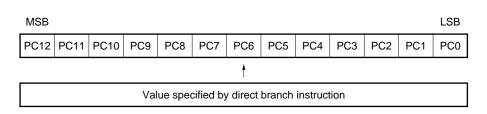

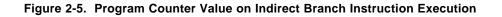

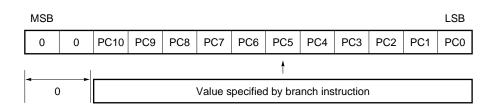

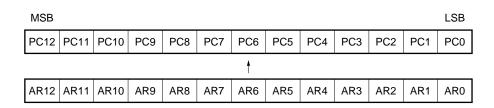

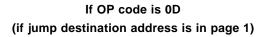

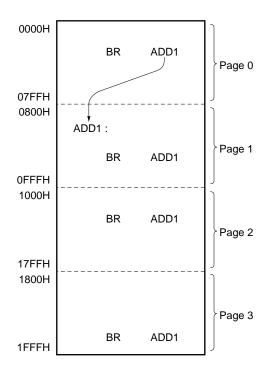

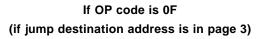

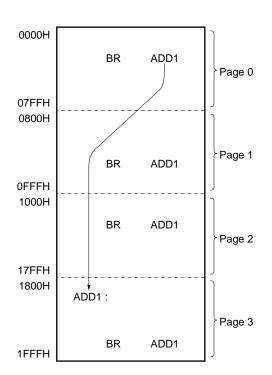

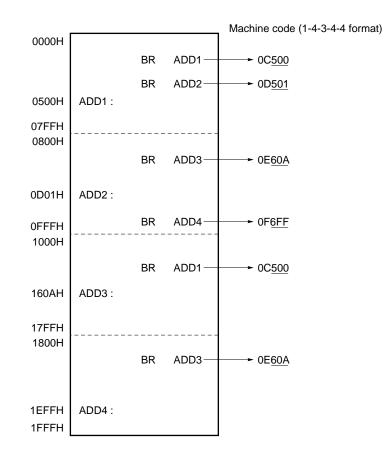

|        | 2.2.2   | On branch instruction (BR) execution                                       |

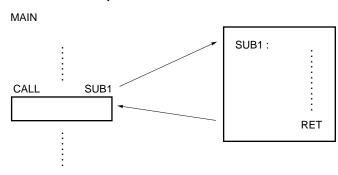

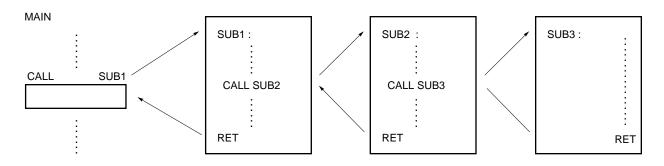

|        | 2.2.3   | On subroutine call instruction (CALL) execution                            |

|        | 2.2.4   | On return instruction (RET, RETSK, or RETI) execution                      |

|        | 2.2.5   | On table reference instruction (MOVT) execution                            |

|        | 2.2.6   | On skip instruction (SKE, SKGE, SKLT, SKNE, SKT, or SKF) execution         |

|        | 2.2.7   | On accepting interrupt                                                     |

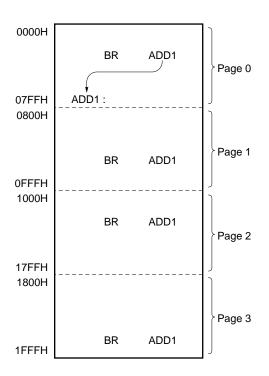

| CHAPTE | R 3 PR  | OGRAM MEMORY (ROM) 29                                                      |

| 3.1    | Progra  | am Memory Configuration                                                    |

| 3.2    | -       | am Memory Function                                                         |

|        | 3.2.1   | Storing program                                                            |

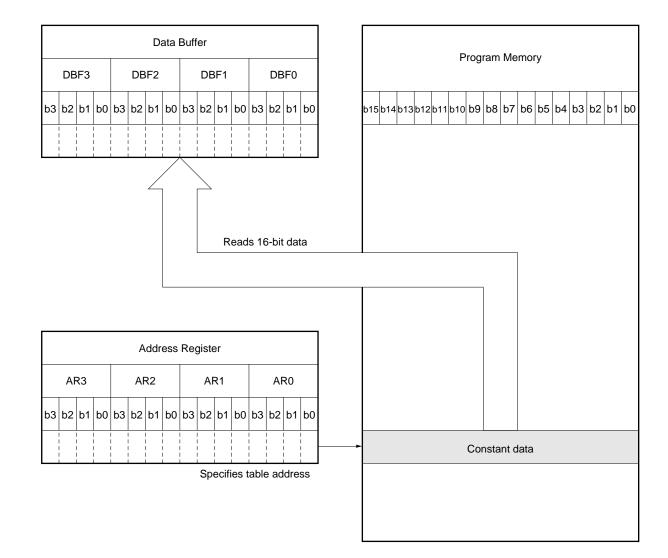

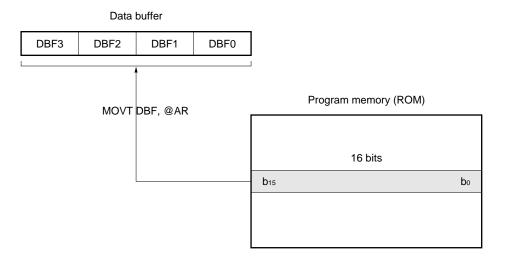

|        | 3.2.2   | Table reference                                                            |

| CHAPTE | R4 DA   | TA MEMORY (RAM) 41                                                         |

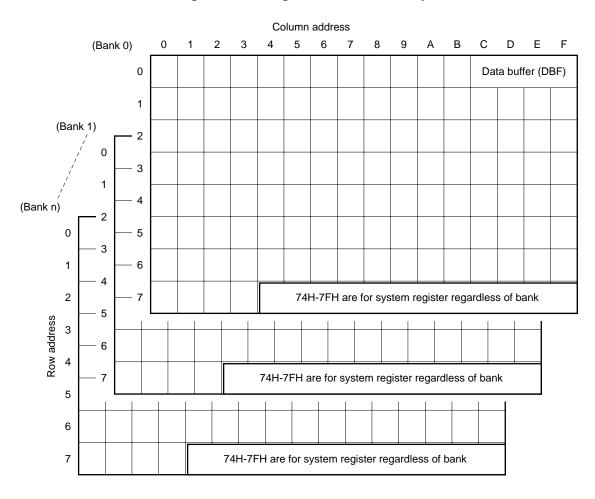

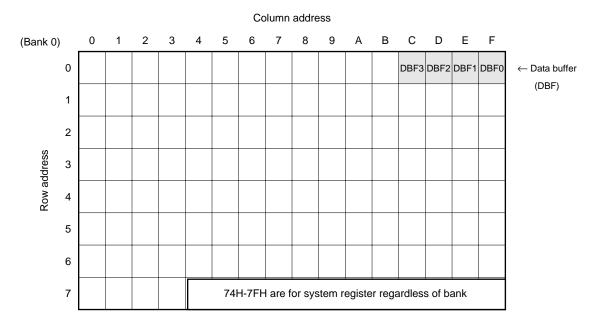

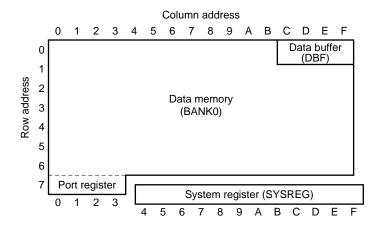

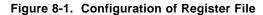

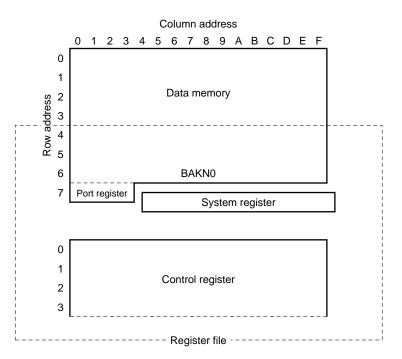

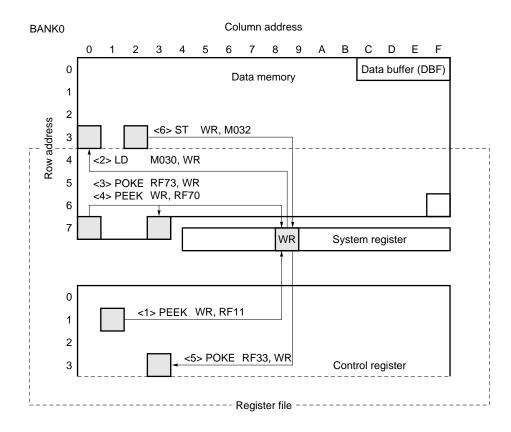

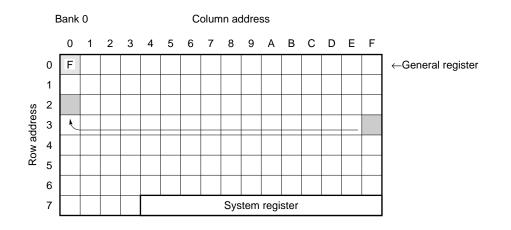

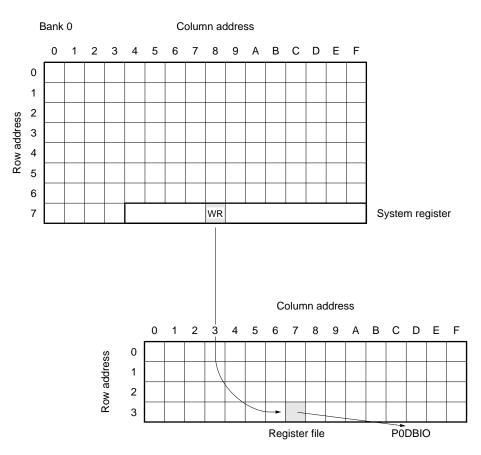

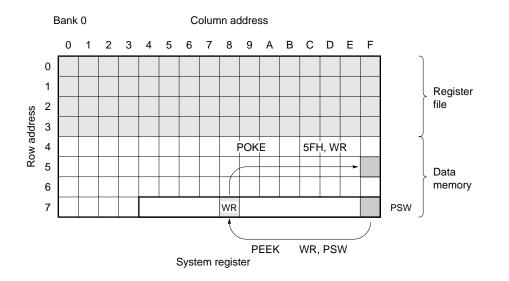

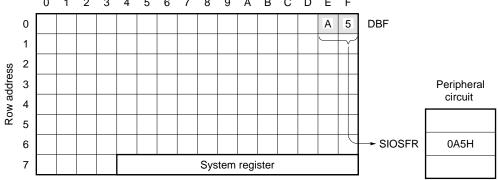

| 4.1    | Data N  | Anticipation 42                                                            |

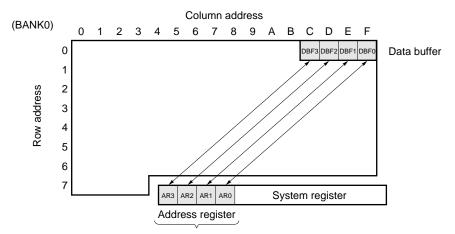

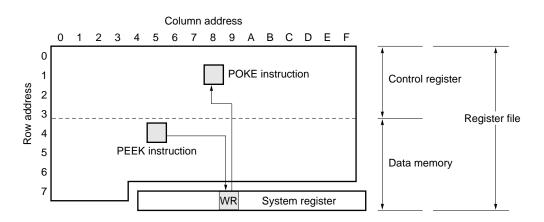

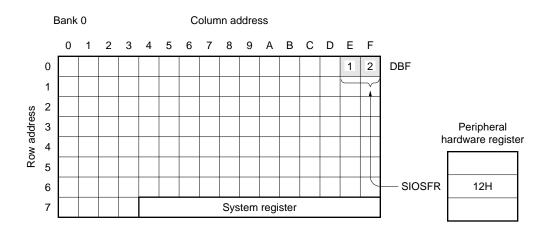

|        | 4.1.1   | System register configuration                                              |

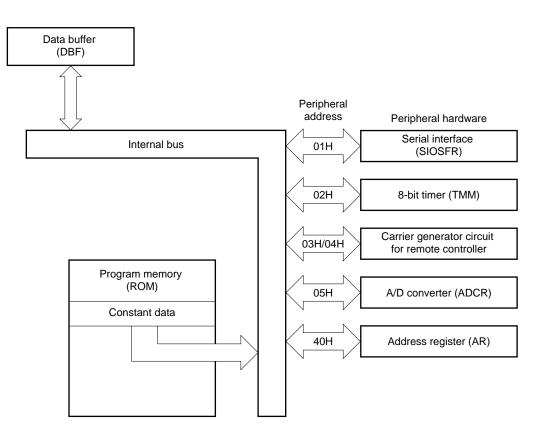

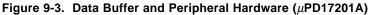

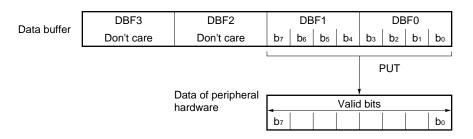

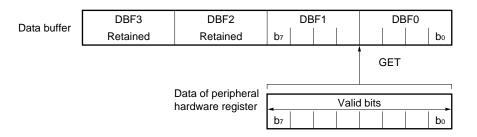

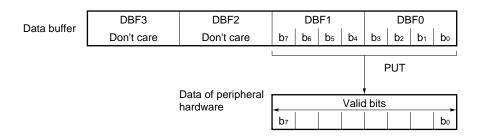

|        | 4.1.2   | Data buffer (DBF)                                                          |

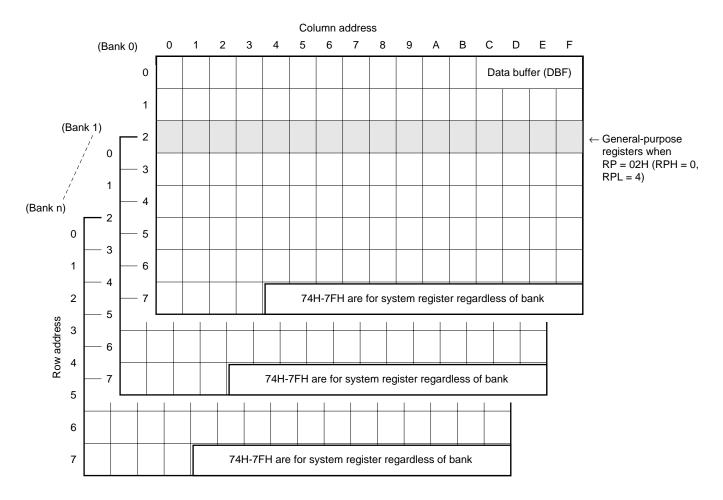

|        | 4.1.3   | General register                                                           |

|        | 4.1.4   | Port register                                                              |

| CHAPTE | R 5 ST  | ACK 45                                                                     |

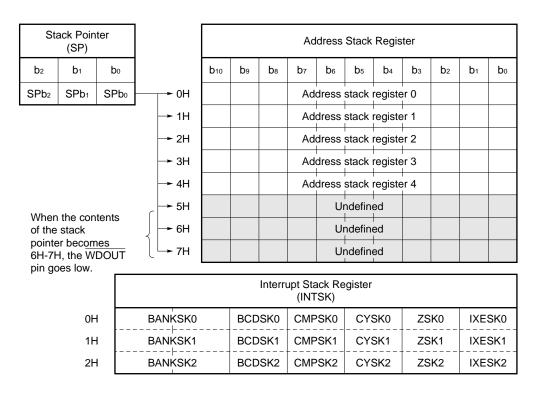

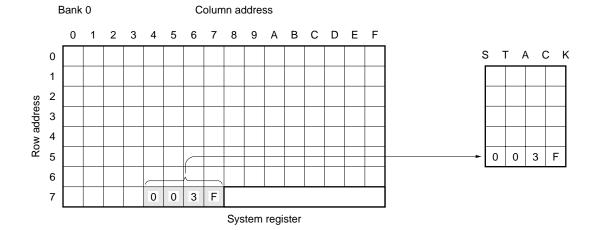

| 5.1    | Config  | juration of Stack                                                          |

| 5.2    | Functi  | on of Stack                                                                |

| 5.3    | Addres  | ss Stack Registers                                                         |

| 5.4    | Interru | ipt Stack Register                                                         |

| 5.5    | Stack   | Pointer (SP) and Interrupt Stack Register 47                               |

| 5.6    | Stack   | Operation When Subroutine or Table Reference Instruction                   |

|        | Is Exe  | cuted or When Interrupt Is Accepted 48                                     |

|        | 5.6.1   | When subroutine call (CALL) or return (RET, RETSK) instruction is executed |

|        | 5.6.2   | When table reference instruction (MOVT DBF, @AR) is executed               |

|        | 5.6.3   | When interrupt is accepted or return instruction (RETI) is executed        |

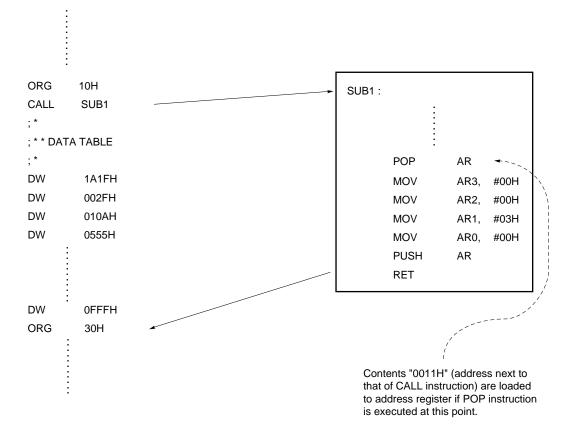

| 5.7    | Nestin  | g Level of Stack, and PUSH and POP Instructions 49                         |

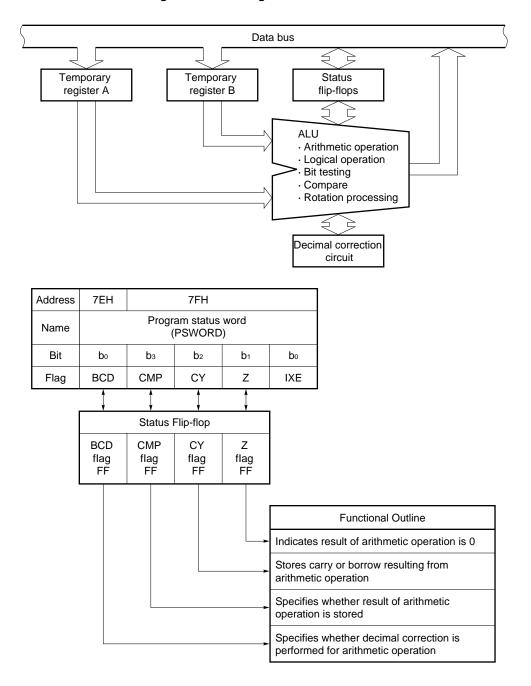

| .2       Add         6.2.       6.2.         6.3       6.3.         6.3       6.3.         6.4       Bar         .5       Ind         6.5.       6.5.         6.6       6.6.         6.7       Pro         6.7       6.7.         6.7       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.8.       6.8.         6.8.       6.8.         6.7.       6.8.         6.8.       6.8.         7.1       Gei         7.2       Gei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2       Address register function         ndow Register (WR)         1       Window register configuration         2       Window register function         2       Window register function         nk Register (BANK)         ex Register (IX)         1       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         5       General register pointer configuration         6       General register pointer function         9       gram Status Word (PSWORD)         1       Program status word configuration         2       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         8       Reserved words of system registers                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2.<br>6.3.<br>6.3.<br>6.3.<br>6.3.<br>6.3.<br>6.5.<br>6.5.<br>6.5.<br>6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>6.8.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2       Address register function         indow Register (WR)         1       Window register configuration         2       Window register function         2       Window register function         2       Window register function         3       KRegister (BANK)         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         3       When MPE = 0, IXE = 1 (data memory address index modification)         4       When MPE = 0, IXE = 1 (data memory address index modification)         5       General register pointer configuration         6       General register pointer configuration         9       General register pointer function         9       Word (PSWORD)         1       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers       1         1       Reserved words of system registers |

| <ul> <li>.3 Wir</li> <li>6.3.</li> <li>6.3.</li> <li>6.3.</li> <li>6.3.</li> <li>6.3.</li> <li>6.5.</li> <li>6.5.</li> <li>6.5.</li> <li>6.5.</li> <li>6.5.</li> <li>6.6.</li> <li>6.6.</li> <li>6.7.</li> <li>6.8.</li> <li>6.8.&lt;</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | addow Register (WR)         1       Window register configuration         2       Window register function         2       Window register function         2       Window register function         4       Register (IX)         1       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         heral Register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         gram Status Word (PSWORD)         1       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers         1       Reserved words of system registers         2       Handling system register fixed to "0"                                                                                                |

| 6.3.<br>6.3.<br>6.3.<br>6.5.<br>6.5.<br>6.5.<br>6.5.<br>6.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1       Window register configuration         2       Window register function         2       Window register function         2       Register (BANK)         ex Register (IX)       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         1       General register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         gram Status Word (PSWORD)       Image: Status Word (PSWORD)         1       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers       Image: Status to "0"         1       Reserved words of system registers         2       Handling system register fixed to "0"                                                                             |

| 6.3.<br>6.4 Bar<br>5 Ind<br>6.5.<br>6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.6.<br>6.7 Pro<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>7 TER 7<br>7 TER 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>2 Window register function</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| .4       Bar         .5       Ind         .5.       6.5.         .6.5.       6.5.         .6.6       6.6.         .7       Pro         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.7.       6.7.         6.8.       6.8.         7.1       Gei         7.1       Gei <tr td=""> <tr td="">      7</tr></tr>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ak Register (BANK)         ax Register (IX)         1       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         5       General register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         gram Status Word (PSWORD)       Image: Status Word (PSWORD)         1       Program status word configuration         2       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers       Image: System register fixed to "0"         1       Reserved words of system registers         2       Handling system register fixed to "0"                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| .5 Ind<br>6.5.<br>6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.6.<br>6.7 Pro<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>6.8.<br>7 TER 7<br>7 TER 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ex Register (IX)         1       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         https://docs.org/line       Index register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         gram Status Word (PSWORD)       Index enable flag (IXE)         1       Program status word configuration         2       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers       Index engister fixed to "0"         1       Reserved words of system register fixed to "0"                                                                                                                                                                                                      |

| 6.5.<br>6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.6.<br>6.7<br>6.7.<br>6.7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1       Index register and data memory row address pointer functions         2       When MPE = 0, IXE = 0 (no data memory modification)         3       When MPE = 1, IXE = 0 (diagonal indirect transfer)         4       When MPE = 0, IXE = 1 (data memory address index modification)         4       When MPE = 0, IXE = 1 (data memory address index modification)         6       Intervention         7       General register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         9       gram Status Word (PSWORD)         1       Program status word configuration         2       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         es on Using System Registers         1       Reserved words of system registers         2       Handling system register fixed to "0"                                                                                                                                                   |

| 6.5.<br>6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>6.8.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>When MPE = 0, IXE = 0 (no data memory modification)</li> <li>When MPE = 1, IXE = 0 (diagonal indirect transfer)</li> <li>When MPE = 0, IXE = 1 (data memory address index modification)</li> <li>meral Register Pointer (RP)</li> <li>General register pointer configuration</li> <li>General register pointer function</li> <li>gram Status Word (PSWORD)</li> <li>Program status word configuration</li> <li>Program status word function</li> <li>Index enable flag (IXE)</li> <li>Zero (Z) and compare (CMP) flags</li> <li>Carry flag (CY)</li> <li>Binary coded decimal flag (BCD)</li> <li>Notes on executing arithmetic operation</li> <li>Reserved words of system registers</li> <li>Reserved words of system registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5.<br>6.5.<br>6.6.<br>6.6.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7.<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>When MPE = 1, IXE = 0 (diagonal indirect transfer)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5.<br>6.6<br>6.6.<br>6.7<br>7 Pro<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.8.<br>6.8.<br>6.8.<br>7 EXER 7<br>7 E | <ul> <li>When MPE = 0, IXE = 1 (data memory address index modification)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| .6 Ger<br>6.6.<br>6.6.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7.<br>6.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | heral Register Pointer (RP)         1       General register pointer configuration         2       General register pointer function         2       gram Status Word (PSWORD)         1       Program status word configuration         2       Program status word function         3       Index enable flag (IXE)         4       Zero (Z) and compare (CMP) flags         5       Carry flag (CY)         6       Binary coded decimal flag (BCD)         7       Notes on executing arithmetic operation         8       on Using System Registers         1       Reserved words of system registers         2       Handling system register fixed to "0"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |